PCIe低功耗(Low Power)

PCI Express(PCIe)已经从一个被认为耗电量大的技术演变为一个非常高效、低功耗的I/O技术。随着移动设备和物联网设备的普及,低功耗成为了关键需求。PCIe规范的持续演进不仅提高了性能,还显著降低了功耗,以满足各种应用的不同需求。尤其是自PCIe 3.0规范以来,PCI-SIG致力于在接口活跃时减少功耗,以实现更好的平台电源管理。

主要功耗状态

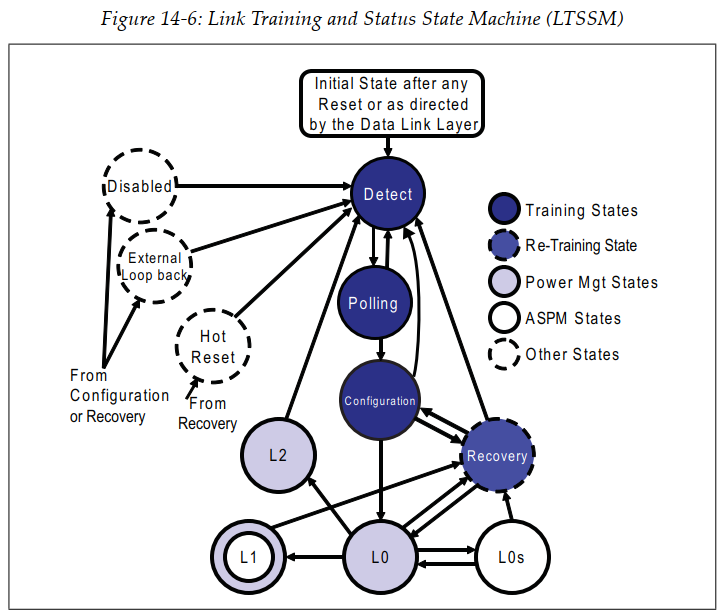

- L0状态:正常操作状态,链路正常运行并传输数据。典型功耗:400-500mW(PCIe 4.0 x4 PHY)。

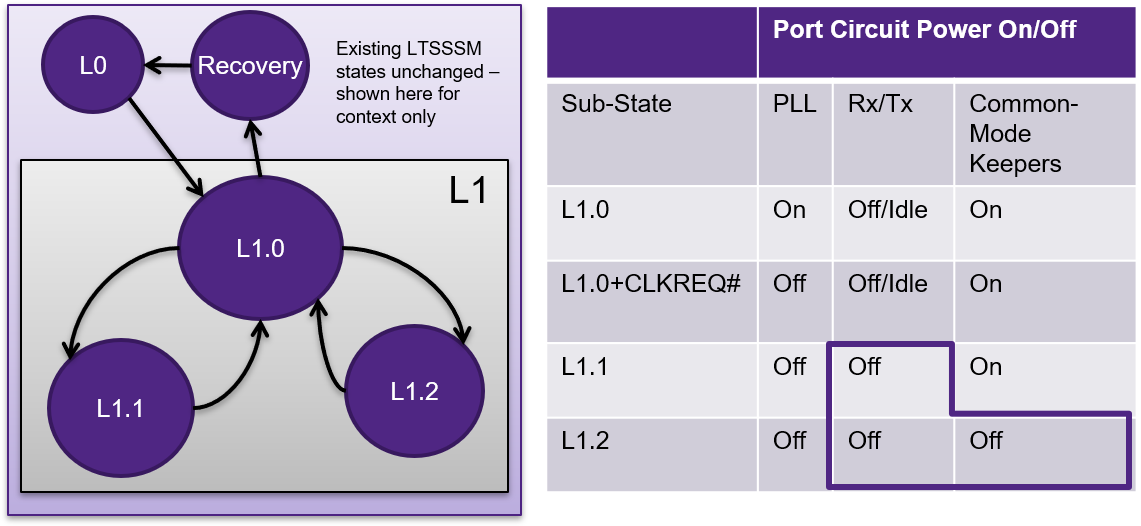

- L1状态:链路没有数据传输的状态,部分PCIe收发器逻辑关闭,以节省电力。子状态包括L1.0、L1.1和L1.2,功耗逐级降低,但退出延迟增加。

- L2状态:与L3状态相同,但电源尚未被移除(尚未断电)。

- L3状态:设备已断电,不消耗功率。

- L0s状态:链路在一个方向上可能有数据传输,另一方向上的收发器可以闲置,进一步降低功耗。链路两端的设备可以各自独立地闲置其发送器。

L1子状态

为了满足移动设备快速响应和低功耗的需求,PCI-SIG引入了L1子状态(L1 sub-states),以实现近乎零功耗的活跃状态。L1子状态通过增加现有PCIe引脚(CLKREQ#)的功能来提供简单的信号协议,使得PCIe收发器可以关闭其高速电路并依靠新的信号唤醒它们。

当L1.0状态时,PLL:开启,Rx/Tx:关闭/空闲,Common Mode Keepers(公共模式保持器):开启。其他L1.1、L1.2状态同理。

PLL、Rx/Tx,公共模式保持器他们是什么,之间有什么关系,为什么关闭他们就能发挥作用?

PLL(锁相环,Phase-Locked Loop):是一种电子电路,能够稳定产生高频时钟信号。

PLL用于生成和维持链路中各个组件同步所需的适中信号,确保数据传输的时序准确性。即PLL为接收器(Rx)和发送器(Tx)提供稳定的时钟信号。

Rx(接收器,Receiver):用来接收来自PCIe链路信号的组件。

Rx负责捕获和解码从链路另一端发送过来的数据包,并将其转换为适合处理器或存储器读取的格式。

Tx(发送器,Transmitter):用来发送信号到PCIe链路的组件。

Tx负责将处理器或存储器提供的数据包编码并发送到链路的另一端。

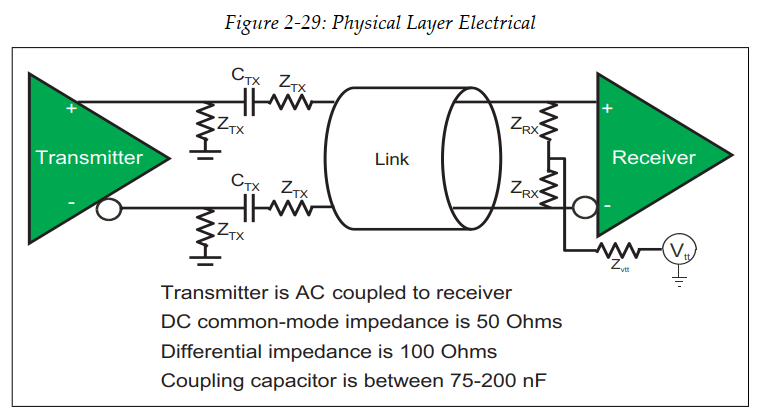

Common Mode Keepers(公共模式保持器):公共模式保持器是一种电路,用于维持差分信号的公共模式电压。

在PCIe链路中,公共模式保持器帮助保持差分信号对的公共模式电平,防止电平漂移,从而保证信号的完整性和可靠性。

公共模式保持器与Rx和Tx一起工作,确保差分信号在传输过程中保持一致的公共模式电平,特别是在低功耗状态(如L1.1和L1.2)下更为重要。

对于Rx/Tx中的Idle(空闲)和Off状态的理解,既然都Idle了,为什么不直接Off呢?

在Idle(空闲)状态下,Rx和Tx电路仍然保持激活状态,但不进行实际的数据传输。

特点:

电路仍然通电:虽然没有数据传输,但电路保持通电,能够快速恢复到传输状态。

快速唤醒:从Idle状态恢复到活跃状态(L0)的时间非常短,几乎可以立即响应数据传输请求。

适用场景:适用于需要频繁进入和退出低功耗模式的场景,如处理器与高速外设之间的通信。

功耗:比关闭状态略高,但比传输数据时的功耗低得多。

在Off(关闭)状态下,Rx和Tx电路完全关闭,断开电源以节省能量。

特点:

- 电路断电:所有相关电路完全断电,不会消耗任何静态功耗。

- 较长的唤醒时间:从Off状态恢复到活跃状态(L0)需要更长的时间,因为需要重新启动和初始化电路。

- 适用场景:适用于长时间不需要数据传输的场景,如设备待机或深度睡眠模式。

功耗:最低,没有任何静态功耗。

为什么使用Idle而不是直接Off?

在许多应用中,如高性能计算或实时系统,需要在极短时间内响应数据传输请求。从Idle状态恢复比从关闭状态(Off)恢复更快,可以减少延迟,提高系统响应速度。

快速响应需求:在许多应用中,如高性能计算或实时系统,需要在极短时间内响应数据传输请求。从Idle状态恢复比从关闭状态(Off)恢复更快,可以减少延迟,提高系统响应速度。

频繁切换场景:在一些系统中,Rx和Tx频繁地在数据传输和非传输状态之间切换。如果每次都关闭和重新启动电路,会引入额外的功耗和延迟。保持Idle状态可以在确保低功耗的同时,保持较高的响应速度。

电路稳定性:频繁关闭和启动电路可能导致电路稳定性下降和寿命缩短。Idle状态下的电路仍保持活跃,减少了反复启动带来的潜在问题。

总结

- Idle状态:保持电路通电,但不进行数据传输。适用于需要快速响应和频繁切换的场景。

- Off状态:电路完全断电,最大限度地节省能量。适用于长时间不需要数据传输的场景。

低功耗优势

- 使用L1.1状态,PCIe 4.0 x4物理层在16GT/s速率下的功耗从L0状态下的400-500mW降至20-30mW,减少了约20倍。

- 使用L1.2状态,功耗进一步降至2-3mW,减少了约10倍。

功耗管理机制

- 延迟容忍报告(LTR):允许主机决定在响应设备中断前的等待时间,以协调多个设备并最大化系统的功耗优化。

- CLKREQ#引脚:通过增加此引脚的功能来实现低功耗信号协议,使PCIe收发器能够关闭其高速电路,并在需要时快速唤醒。

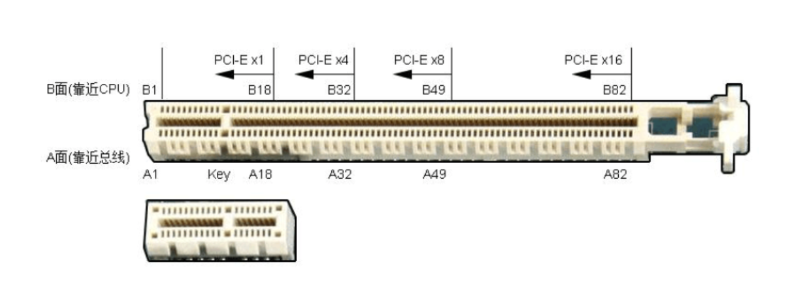

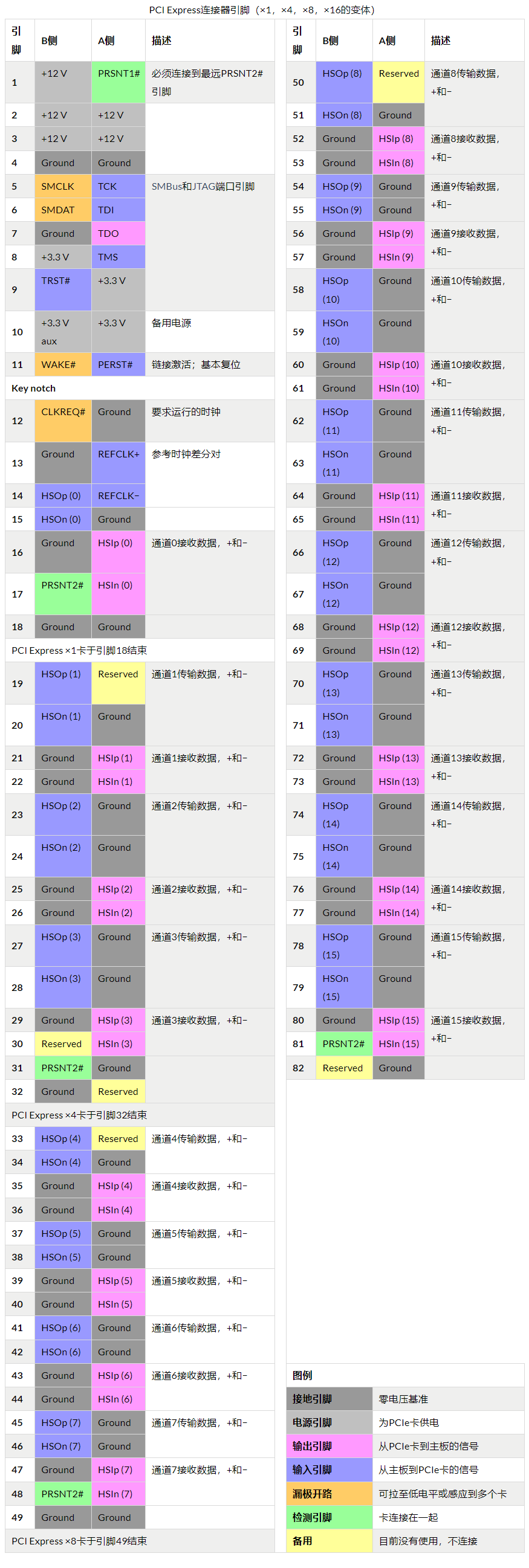

PCIe总线引脚,PCIe卡两侧导线

引脚定义

下表列出在边缘连接器上的PCI Express卡两侧的导线。在印刷电路板(PCB)的焊接侧为A侧,并且组件侧的B侧。PRSNT1# 和PRSNT2# 引脚必须比其余稍短,以确保热插入卡完全插入。该WAKE# 引脚采用全电压唤醒计算机,但必须拉高从备用电源,以表明该卡是能够唤醒。

L状态是主动进入还是被动进入,若被动进入,跟什么有关系呢?设置什么才能让它进行切换?